# FEATURES

- A highly featured PSTN Interface (COIC, FXO, DAA, Trunk Interface) in a single 12mm high SIL device.

- +5V or +3.3V supply.

- Transformer isolation providing high common-mode rejection (CMRR) for use in un-grounded systems.

- Highly integrated with on-board loop switch and diode bridge.

- Loop start circuit, ringing detect, line detection and parallel phone detect.

- On-hook reception.

- Meets requirements of FCC Pt68.

- Low cost power cross protection.

- Programmable d.c. mask, line and network impedances, allows use in any market.

- Silver Telecom "design-in" assistance.

## DESCRIPTION

The Ag2130 is a self-contained highly integrated PSTN Interface Circuit in a single SIL module, which complies with ROHS requirements.

In addition to the features listed, the Ag2130 allows flexible programming of many functions, including the dc voltage mask and impedances. The Ag2130 meets international safety and regulatory requirements.

The device requires a minimum of external components and has been specified for ease of use, to allow reduced time to market.

The Ag2130 is designed for all applications, including those where there is a high level of common mode interference, such as PABX, long loop applications and systems without a ground connection.

Approved to: EN 60950-1:2001 IEC60950-1: First Edition 2001 AS/NZ60950-1: 2003 UL60950-1: 2003 1<sup>st</sup> Edition CSA 22.2 No.60950-1-03 1<sup>st</sup> Edition

# **Ordering Information**

Ag2130S Fully featured Trunk in SIL package (RoHS Compliant)

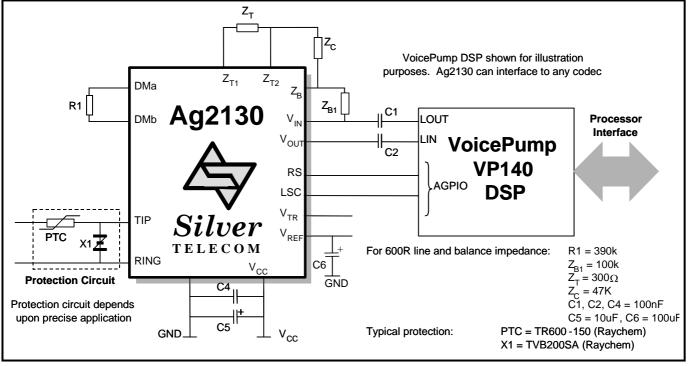

Figure 1: Ag2130S - SIL Packaging Format

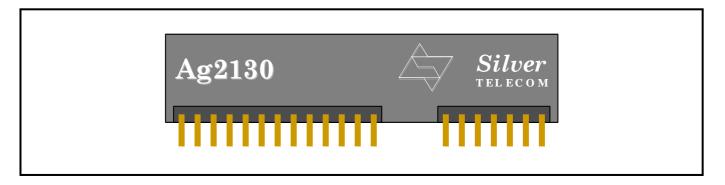

Figure 2: Functional Block Diagram

#### 1.0 Pin Description

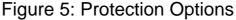

#### 1.1 SIL Pin-Out

| Pin # | Name             | Description                                                                                                                                                                                  |  |  |  |  |  |  |

|-------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 1     | RING (B)         | Ring. Connects to the subscriber line Ring.                                                                                                                                                  |  |  |  |  |  |  |

| 2     | TIP (A)          | Tip. Connects to the subscriber line Tip.                                                                                                                                                    |  |  |  |  |  |  |

| 3     | CATHODE          | <b>Cathode.</b> For power cross protection connect to protection device cathode.                                                                                                             |  |  |  |  |  |  |

| 4     | ANODE            | <b>Anode.</b> For power cross protection connect to protection device anode.                                                                                                                 |  |  |  |  |  |  |

| 5     | GATE             | Gate. For power cross protection connect to protection device gate.                                                                                                                          |  |  |  |  |  |  |

| 6     | DMb              | <b>DC Mask b.</b> A resistor is connected between this pin and DMa to adjust the d.c. characteristics of the termination.                                                                    |  |  |  |  |  |  |

| 7     | DMa              | <b>DC Mask a.</b> A resistor is connected between this pin and DMb to adjust the d.c. characteristics of the termination.                                                                    |  |  |  |  |  |  |

| 8     | nc               | No connect. This pin is not used and can be left open circuit.                                                                                                                               |  |  |  |  |  |  |

| 9     | V <sub>IN</sub>  | <b>Audio In.</b> This is the analog input signal from the Codec (which is output on Tip and Ring). Connected via a 100nF capacitor.                                                          |  |  |  |  |  |  |

| 10    | V <sub>OUT</sub> | <b>Audio Out.</b> This is the analog output signal (from Tip and Ring) to the Codec. Connected via a 100nF capacitor.                                                                        |  |  |  |  |  |  |

| 11    | LSC              | <b>Loop switch control.</b> Applying a logic 1 closes the integral loop switch.                                                                                                              |  |  |  |  |  |  |

| 12    | GND              | Analog ground. Normally connected to system ground.                                                                                                                                          |  |  |  |  |  |  |

| 13    | V <sub>cc</sub>  | <b>Positive supply.</b> Must be connected to +5V or +3.3V.                                                                                                                                   |  |  |  |  |  |  |

| 14    | nc               | No connect. This pin is not used and can be left open circuit.                                                                                                                               |  |  |  |  |  |  |

| 15    | Z <sub>B</sub>   | <b>Balance network.</b> The network balance matching components are connected between this pin, $V_{IN}$ and GND.                                                                            |  |  |  |  |  |  |

| 16    | Z <sub>T2</sub>  | <b>2 Wire matching network 2.</b> The 2 wire impedance matching network is connected between this pin and $Z_{T1}$ . The compensation impedance Zc is connected between this pin and $Z_B$ . |  |  |  |  |  |  |

| 17    | Z <sub>T1</sub>  | <b>2 Wire matching network 1.</b> The 2 wire impedance matching network is connected between this pin and $Z_{T2}$ .                                                                         |  |  |  |  |  |  |

| 18    | RS               | <b>Ringing signal.</b> A logic 0 indicates the presence of ringing voltage on the telephone line. Toggles at ringing frequency.                                                              |  |  |  |  |  |  |

| 19    | V <sub>REF</sub> | <b>Reference voltage output.</b> Used with $V_{TR}$ to detect parallel phone. $V_{REF}$ is approximately +V <sub>CC</sub> /2. Connect 100µF to GND from this pin.                            |  |  |  |  |  |  |

| 20    | V <sub>TR</sub>  | <b>Tip/Ring voltage.</b> Indicates the voltage between Tip/Ring. Divided by 220 and relative to Vref.                                                                                        |  |  |  |  |  |  |

#### 2.0 Line Interfacing

The Ag2130 line interface provides a flexible and robust interface to the telephone line. It has been designed to meet regulatory standards whilst providing a space and power efficient solution.

#### 2.1 D.C. Termination.

Any equipment terminating a telephone line must present the correct d.c. resistance to the line. This ensures that the correct loop current flows for detection of the off-hook condition. It avoids excessive power dissipation in the Subscriber Line Interface (SLIC) and the Subscriber's equipment and minimises the size of power supply needed to drive the SLIC.

The Ag2130 has been designed to meet the requirements of many network operators. This is done by making the d.c. characteristic adjustable. This is controlled by connecting the DM pins on the line side of the circuit. Table 1 shows how these are connected.

| Table 1 Set Up of the DM Pins | , |

|-------------------------------|---|

|-------------------------------|---|

| Market                                | DMa                                      | DMb |  |  |  |

|---------------------------------------|------------------------------------------|-----|--|--|--|

| North America<br>(EIA 464, Resistive) | Connect together throug<br>390K resistor |     |  |  |  |

| Europe (CTR21)                        | Connect together through 390K resistor   |     |  |  |  |

| Far East                              | Connect together through 390K resistor   |     |  |  |  |

#### 2.2 Signalling and Loop Status.

The Ag2130 provides facilities to monitor and control the telephone line. This allows the device to be used with a variety of loop signalling schemes and minimises the number of external components needed to implement a complete line interface.

In order to implement ground start applications please contact Silver Telecom or our local representative.

#### 2.2.1 The On-Board Loop Switch

The Ag2130 implements the loop start protocol when initiating and answering a call. This means that a switch must be closed to allow loop current to flow, signalling to the SLIC that the terminating equipment has gone "off-hook". This has been done historically by a relay. The Ag2130 uses an integral optically isolated switch to do this, eliminating the need for an external relay, so space and cost is saved for the user.

The on-board Loop Switch is controlled by the LSC pin. A logic 1 applied to the pin closes the loop switch. This is done when the terminating equipment wishes to begin a call or in response to the reception of the ringing signal. The LSC pin can be controlled by the output drive pins of a codec or from a micro controller device.

#### 2.2.2 Ringing Detection and Sensitivity.

The terminal equipment must be capable of detecting and responding to an incoming call in the same way as a telephone set. The termination circuitry must, therefore, detect the presence of the ringing signal.

The Ag2130 provides an output, RS, which indicates the presence of ringing by switching from a logic 1 to logic 0. The RS output will toggle at the ringing frequency. A capacitor to ground can also be added if ringing cadence is needed rather than the ringing frequency.

The sensitivity to ringing is set internally to  $22V_{\text{RMS}}$  when  $V_{\text{CC}}$  is +5V.

#### 3.0 The 2-4 Wire (Hybrid) Conversion.

The Ag2130 transmits and receives balanced 2-wire analog signals at the Tip and Ring connections. These are converted to a ground referenced output at  $V_{OUT}$  and from a ground referenced signal at  $V_{IN}$ .

$V_{_{OUT}}$  and  $V_{_{\rm IN}}$  are normally connected to a codec (via d.c. blocking capacitors) for conversion to and from a Pulse Code Modulated (PCM) stream.

#### 3.1 Transmit and Receive Gain.

The off-hook gain in both the transmit and receive directions is set at typically 0dB. Any gain adjustments can be made using the codec functionality. This is either by hardware or software depending upon the codec used.

# Ag2130 Low cost pstn interface

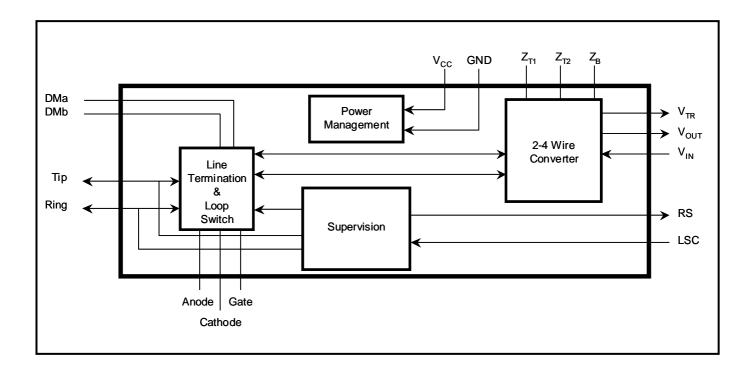

| eg. | 2-wire<br>Impedance | Z <sub>T</sub>  | Zc             | Network<br>Balance<br>Impedance | Z <sub>b1</sub> | Z <sub>b2</sub> | Z <sub>b3</sub> | C3    | Notes                                    |

|-----|---------------------|-----------------|----------------|---------------------------------|-----------------|-----------------|-----------------|-------|------------------------------------------|

| 1   | 600Ω                | 300Ω            | 47K            | 600Ω                            | 100K            | 0R              |                 |       | USA Short Line,<br>Far East, Middle East |

| 2   | CTR21               | 750R//<br>220nF | 68K//<br>680pF | CTR21                           | 220K//<br>680pF | 5.1K            |                 |       | Europe                                   |

| 3   | 900Ω                | 620Ω            | 62K            | 900Ω                            | 220K            | 0R              |                 |       | USA Long Line, Brazil                    |

| 4   | 600Ω                | 300Ω            | 47K            | 100R<br>+1K//100nF              | 39K             | 39K             | 0R              | 1.5nF | Japan                                    |

Table 2: Line and Network Balance Impedance Examples

#### 3.2 The 2 Wire Impedance

The input impedance,  $Z_{IN}$ , of the Ag2130 can be programmed. This is achieved by connecting an impedance matching network between  $Z_{T1}$  and  $Z_{T2}$ . This network is the line impedance to be matched minus 300 $\Omega$ . For example to match 600 $\Omega$ , fit a 300 $\Omega$  resistor. Other common line impedances, and the corresponding programming components are listed in Table 2.

In addition to the programming network, an impedance,  $Z_C$  must be fitted between ZT2 and Zb to provide gain and frequency compensation.

An alternative method of programming the 2 wire impedance is to choose a codec where the internal filter characteristics can be programmed to provide the correct matching. In order to generate the filter coefficients a model of the Ag2130 must be used. This file, in .CIR format is available on request from Silver Telecom or one of our representatives.

Full details on how the Codec is programmed must be obtained from the Codec manufacturer.

#### 3.3 Network Balance Impedance

The setting of the network balance impedance is very similar to that of the 2 wire impedance. Again this can be done by programming of the codec, using the .CIR file, or it can be done by hardware components.

#### 3.4 On-Hook Reception

The need for data exchange when on-hook is becoming increasingly common. This may be required for Caller Line I.D. or for telemetry purposes. The

Figure 3: Line Impedance and Network Balance Components

Ag2130 can receive signals when on-hook, presenting a high impedance to the line. I.e. whilst drawing a very small current ( $5\mu A$  approx) from the line.

#### 3.5 Ringer Load Networks

The "dummy ringer" is usually a capacitive/resistive load which is connected across TIP/RING. During a call it is of sufficiently high impedance not to affect the operation of the interface. The Ag2130 meets the dummy ringer requirements for CTR21 (Europe), USA and Asia.

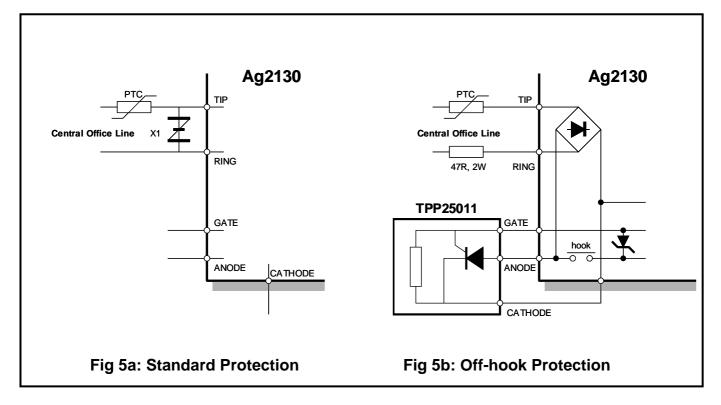

#### 4.0 Device Protection.

Like many of the performance requirements which the Ag2130 must meet, protection for the interface is dependent upon regulatory standards in the market in which the equipment is deployed. Some examples are given below, but these are not exhaustive.

For a more comprehensive overview of protection for line interfaces, refer to our Over-voltage Protection Applications Note. This is may be downloaded from the Silver Telecom web-site (www.silvertel.com) or will be provided by our local representative.

#### 4.1 FCC Pt 68 Requirements.

To withstand the FCC Pt68 longitudinal voltage surge of 1500V no protection is required, as the barrier will withstand 1500V peak voltage to GND.

To withstand the FCC Pt68 metallic surges at 800V

requires a 130V AC varistor (which clamps at 300V which is the maximum rating of the loop switch transistor). A 14mm device should be used to withstand the two 100A 10/560us surges.

Examples of suitable devices are:-Joyin JVR-14N201K; Walsin VZ14D201KBS

Note: If varistors to ground are used for added protection (e.g. more than 1500V) customers should be aware that the FCC test generator for longitudinal tests is rated at up to 1000A.  $10\Omega$ , 2W wire wound surge limiting resistors will also be needed.

#### 4.2 EN/UL60950 Protection.

To meet the EN/UL60950 mains cross test  $22\Omega$ , 2W wire wound surge resistors and 0.35A special fuses (Bussman C515 or Littelfuse 220003) in a balanced configuration are required. Alternatively a Teccor F1250T fuse may be used without surge limiting resistors.

It is also possible to use PTC thermistors to meet these tests. The Raychem TR600-150 is designed for this application. See Raychem Application Notes for further details. A typical application is shown in figure 6a.

#### 4.3 Other Standards.

The Ag2130 has provision for low cost mains cross protection (CCITT K21): a  $47\Omega$ , 2W wire wound surge resistor and a PTC thermistor are sufficient to meet regulatory approvals. A suitable device is the Walsin

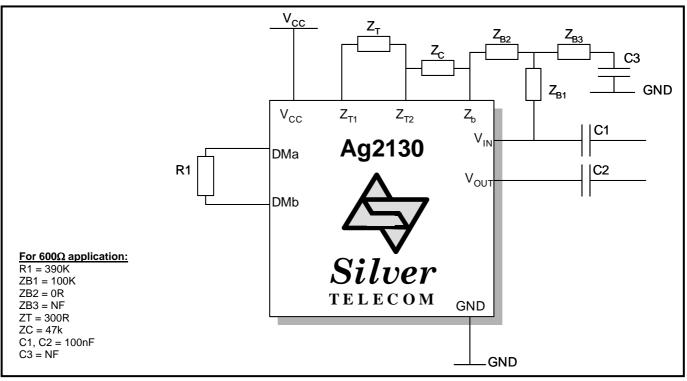

Figure 4: Typical Application

PTD3A350H26. (Metallic protection with a single device is all that is required, as the Ag2130 will withstand longitudinal voltages up to 1000Vrms to ground without additional protection).

As an option, for improved off-hook power cross protection, the Ag2130 has been designed to interface directly to the STM TPP25011. This protection arrangement is shown in figure 6b.

#### 5.0 Regulatory Standards

There are some aspects of international standards that are not fully met by the Ag2130. These are shown below. It is Silver Telecom's policy to bring to the attention of customers all known exceptions.

The Ag2130 meets the requirements of EN60950-1: 2001 paragraph 6.1.2.1 for all countries <u>except</u> Norway, Sweden and Finland. Please contact Silver Telecom if the product is needed for these countries.

The Ag2130 has been approved to the following safety standards: EN 60950-1:2001 IEC60950-1: First Edition 2001 AS/NZ60950-1: 2003 UL60950-1: 2003  $1^{st}$  Edition CSA 22.2 No.60950-1-03  $1^{st}$  Edition In order to maintain this approval when the Ag2130 is incorporated into a host system care must be taken to maintain the user protection provided in the Ag2130 by ensuring adequate separation of the line side circuitry and components from the protected circuit so that the barrier is not compromised. The system should be housed in a fire enclosure made of a suitable flame retardant material.

For USA and Canada the line cord connecting the system to the network must have minimum 26AWG conductors.

User/Network safety from mains power voltage (EN60950 paragraphs 2.1.1 and 6.1) must be provided externally by a power supply with reinforced or double insulation.

#### 6.0 Layout

Signal tracks should be kept as short as possible. Special attention should be paid to DMa, DMb and  $Z_B$  as these are sensitive nodes.

#### Absolute Maximum Ratings\* 70

| 1.0        | Absolute maximum natings                                |    |

|------------|---------------------------------------------------------|----|

| All Voltag | ages are with respect to ground unless otherwise stated | J. |

|   | Parameter                                                 | Sym                | Min  | Max  | Units             |

|---|-----------------------------------------------------------|--------------------|------|------|-------------------|

| 1 | DC supply voltage                                         | V <sub>CC</sub>    | -0.3 | 6.0  | V                 |

| 2 | DC battery voltage present between Tip and Ring (on-hook) | $V_{TR}$           |      | 300  | V                 |

| 3 | Maximum voltage on programmable pin, LSC                  |                    | -0.3 | 6.0  | V                 |

| 4 | Maximum power dissipation @ 25°C                          | P <sub>TRUNK</sub> |      | 0.75 | W                 |

| 5 | Maximum loop current (continuous)                         | I <sub>LOOP</sub>  |      | 90   | mA                |

| 6 | Maximum ringing current (for 0.5 second)                  | I <sub>RING</sub>  |      | 185  | mA <sub>RMS</sub> |

| 7 | Storage Temperature                                       | Ts                 | -40  | +100 | °C                |

\*Exceeding the above ratings may cause permanent damage to the product. Functional operation under these conditions is not implied. Maximum ratings assume free air flow.

# **8.0 Recommended Operating Conditions\*** All Voltages are with respect to ground unless otherwise stated.

|   | Parameter                                    | Symbol                                | Min    | Тур      | Max          | Units  |

|---|----------------------------------------------|---------------------------------------|--------|----------|--------------|--------|

| 1 | DC supply voltage (+5V operation)            | V <sub>CC</sub>                       | 4.75   | 5.0      | 5.25         | V      |

| 2 | DC supply voltage (+3.3V operation)          | V <sub>CC</sub>                       | 3.13   | 3.3      | 3.47         | V      |

| 3 | DC battery voltage on Tip and Ring (on-hook) | V <sub>TIP</sub><br>V <sub>RING</sub> | 0<br>0 | 0<br>-48 | -120<br>-120 | V<br>V |

| 4 | DC loop current                              | I <sub>LOOP</sub>                     | 0      | 25       | 85           | mA     |

| 5 | Operating Temperature                        | T <sub>OP</sub>                       | 0      | 25       | 70           | OO     |

\*Typical figures are at 25°C with nominal +5V or +3.3V supplies and are for design use only.

# 9.0 DC Electrical Characteristics.

|    | Characteristic                                                 | Sym                                | Min  | Typ <sup>2</sup> | Max        | Units    | Test Comments <sup>1</sup>                 |

|----|----------------------------------------------------------------|------------------------------------|------|------------------|------------|----------|--------------------------------------------|

| 1  | Supply current, on-hook <sup>3</sup>                           | I <sub>CC</sub>                    |      | 2.5              | 4.0        | mA       |                                            |

| 2  | Loop current range                                             | I <sub>LOOP</sub>                  | 14.0 |                  | 85.0       | mA       |                                            |

| 3  | Status output, RS<br>Output low voltage<br>Output high voltage | V <sub>OL</sub><br>V <sub>OH</sub> | 4.5  |                  | 0.4        | V<br>V   | +5V operation<br>@ 50μA<br>@ -50μA         |

| 4  | Status output, RS<br>Output low voltage<br>Output high voltage | V <sub>OL</sub><br>V <sub>OH</sub> | 2.8  |                  | 0.4        | V<br>V   | +3.3V operation<br>@ 50μA<br>@ -50μA       |

| 5  | Control input, LSC<br>Input low voltage<br>Input high voltage  | V <sub>IL</sub><br>Vi⊦             | 2.5  |                  | 0.5        | V<br>V   | +5V operation                              |

| 6  | Control input, LSC<br>Input low current<br>Input high current  | I <sub>IL</sub><br>I <sub>IH</sub> |      |                  | 200<br>450 | μΑ<br>μΑ | +5V operation                              |

| 7  | Control input, LSC<br>Input low voltage<br>Input high voltage  | V <sub>IL</sub><br>VIH             | 2.5  |                  | 0.5        | V<br>V   | +3.3V operation                            |

| 8  | Control input, LSC<br>Input low current<br>Input high current  | I <sub>IL</sub><br>I <sub>IH</sub> |      |                  | 100<br>300 | μA<br>μA | +3.3V operation                            |

| 9  | Off-hook DC voltage                                            |                                    |      | 5.7              |            | V        | I <sub>LOOP</sub> = 20mA<br>DMa-DMb = 390K |

| 10 | Leakage current, Tip and Ring to analog ground                 | I <sub>LA</sub>                    |      |                  | 35         | μA       | 100V <sub>DC</sub>                         |

| 11 | Leakage current on-hook, Tip to Ring                           | I <sub>LTR</sub>                   |      |                  | 35         | μA       | 100V <sub>DC</sub>                         |

All DC Electrical Characteristics are over the Recommended Operating Conditions with  $V_{CC}$  at +5.0V <u>+</u>5%, unless otherwise stated.

1 For test circuit details please contact Silver Telecom

2 Typical figures are at 25°C with nominal supply and 25mA loop current, unless otherwise stated. These figures are for design aid only.

3 Operating currents are dependent on the users application.

## **10.0 AC Electrical Characteristics.**

|    | Characteristic                                                                           | Sym             | Min      | Тур*       | Max  | Units             | Test Comments <sup>1</sup>                         |

|----|------------------------------------------------------------------------------------------|-----------------|----------|------------|------|-------------------|----------------------------------------------------|

| 1  | Ringing voltage: detect<br>Ringing voltage: no detect                                    | V <sub>RD</sub> | 30       | 26<br>26   | 22   | V <sub>RMS</sub>  | +5V supply<br>17 to 68Hz                           |

| 2  | Ringing voltage: detect<br>Ringing voltage: no detect                                    | $V_{RD}$        | 26       | 22<br>22   | 18   | V <sub>RMS</sub>  | +3.3V supply<br>17 to 68Hz                         |

| 3  | Input Impedance at $V_{IN}$                                                              |                 |          | 100        |      | kΩ                |                                                    |

| 4  | Output impedance at Vout                                                                 |                 |          |            | 10   | Ω                 |                                                    |

| 5  | Voltage gain, 2 Wire to $V_{OUT}$                                                        |                 | -0.5     | 0          | +0.5 | dB                | Off-hook, 1KHz                                     |

| 6  | Voltage gain, $V_{IN}$ to 2 Wire                                                         |                 | -1.0     | -0.5       | 0    | dB                | Off-hook, 1KHz                                     |

| 7  | On-hook gain, 2 Wire to $V_{OUT}$                                                        |                 | -6.8     | -6.3       | -5.8 | dB                | On-hook, 1kHz                                      |

| 8  | Relative gain, referenced to<br>1kHz. 2Wire - V <sub>out</sub> , V <sub>in</sub> - 2Wire |                 | -0.5     |            | +0.5 | dB                | 300 - 3400 Hz                                      |

| 9  | Total harmonic distortion @ 2Wire and V <sub>out</sub>                                   | THD             |          | 0.1        | 1.0  | %                 | @0dBm, 1kHz                                        |

| 10 | Overload distortion @2 Wire and V <sub>out</sub> @+3dBm, 1 kHz                           | OD              |          | 0.5        | 5.0  | %                 | +5V supply<br>+3.3V supply                         |

| 11 | Common mode rejection ratio off-hook                                                     | CMRR            | 70       | 80         |      | dB                | 50 – 500Hz<br>V <sub>CM</sub> = 60V <sub>RMS</sub> |

| 12 | Common mode overload level<br>off-hook                                                   | CMOL            | 250      | 300        |      | V <sub>RMS</sub>  | 50 – 60Hz                                          |

| 13 | Idle channel noise off-hook                                                              | N <sub>C</sub>  |          | 0          | 12   | dBrnC             | @2 Wire &<br>V <sub>OUT</sub>                      |

| 14 | CMRR on-hook                                                                             |                 | 40       | 55         |      | dB                | 50-500Hz                                           |

| 15 | CMOL on-hook                                                                             |                 |          | 300<br>140 |      | V <sub>RMS</sub>  | +5V supply<br>+3.3V supply                         |

| 16 | Idle Noise on-hook                                                                       |                 |          | 23         |      | dBrnC             | @Vout                                              |

| 17 | Power supply rejection ratio<br>At 2 Wire and V <sub>out</sub>                           | PSRR            | 25       |            |      | dB                | Ripple 0.1V,<br>1kHz on V <sub>CC</sub>            |

| 18 | Return loss, 600R                                                                        | RL              | 18       | 35         |      | dB                | 300-3400Hz                                         |

| 19 | Transhybrid loss, 600R                                                                   | THL             | 18<br>21 | 35         |      | dB<br>dB          | 300-3400Hz<br>500-2500Hz                           |

| 20 | Metallic to longitudinal balance                                                         |                 | 60<br>40 | 70<br>70   |      | dB<br>dB          | 200-1000Hz<br>1000-4000Hz                          |

| 21 | Leakage current, Tip or Ring to analog ground                                            | $I_{LA}$        |          |            | 5    | mA <sub>RMS</sub> | 1000V ac                                           |

All AC Electrical Characteristics are over the Recommended Operating Conditions with  $V_{CC}$  at +5.0V <u>+</u>5%, unless otherwise stated.

\*Typical figures are at 25°C with nominal 5V supply and 25mA loop current unless otherwise stated. These figures are for design aid only.

# **Mechanical Specification and Pin Assignation**

# 11.1 Ag2130S – SIL Package